#### **Topic 8**

#### Sequential Circuits<sup>1</sup>

Peter Cheung

Department of Electrical & Electronic Engineering

Imperial College London

Rabaey Chapter 7

URL: www.ee.ic.ac.uk/pcheung/ E-mail: p.cheung@ic.ac.uk

<sup>1</sup> Based on slides from Prentice-Hall

Nov-8-10 E4.20 Digital IC Design Topic 8 - 1

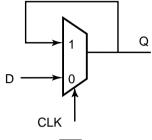

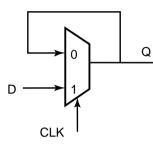

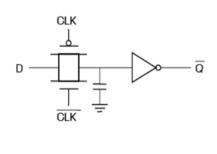

#### **Mux-Based Latch**

#### **Mux-Based Latches**

## Negative latch (transparent when CLK= 0)

## Positive latch (transparent when CLK= 1)

$$Q = \overline{Clk} \cdot Q + Clk \cdot In$$

$$Q = Clk \cdot Q + \overline{Clk} \cdot In$$

Nov-8-10 E4.20 Digital IC Design Topic 8 - 2

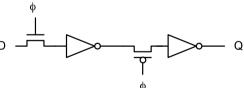

#### **Mux-Based Latch**

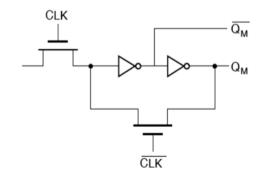

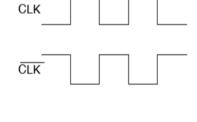

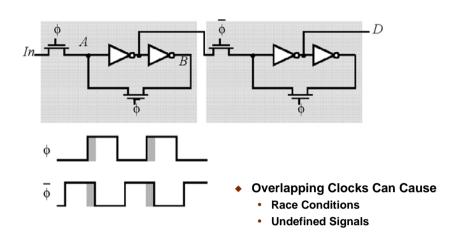

NMOS only

Non-overlapping clocks

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 3

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 4

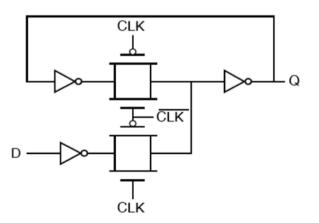

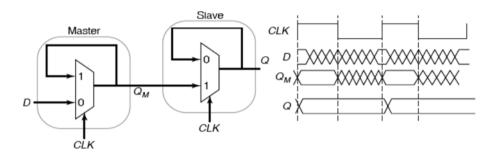

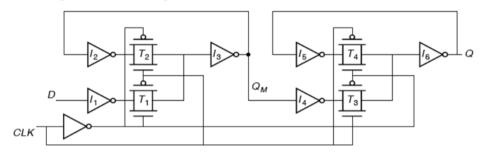

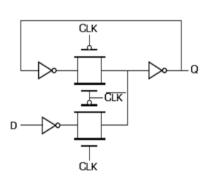

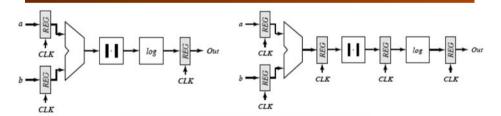

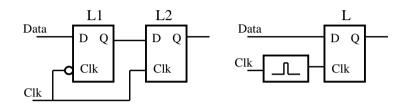

#### **Master-Slave (Edge-Triggered) Register**

Two opposite latches trigger on edge Also called master-slave latch pair

Nov-8-10 E4.20 Digital IC Design Topic 8 - 5

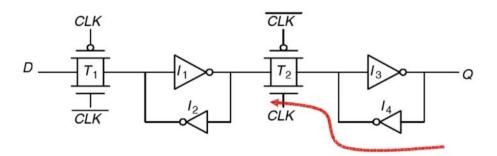

## **Reduced Clock Load Master-Slave Register**

#### **Master-Slave Register**

#### Multiplexer-based latch pair

Nov-8-10 E4.20 Digital IC Design Topic 8 - 6

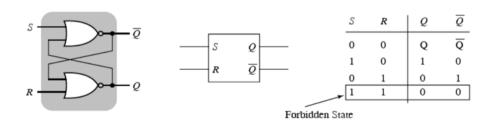

## Overpowering the Feedback Loop — Cross-Coupled Pairs

#### NOR-based set-reset

Nov-8-10 E4.20 Digital IC Design Topic 8 - 7 Nov-8-10 E4.20 Digital IC Design Topic 8 - 8

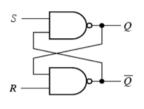

#### **Cross-Coupled NAND**

#### Cross-coupled NANDs

This is not used in datapaths any more, but is a basic building block for memory cell

Nov-8-10 E4.20 Digital IC Design Topic 8 - 9

#### **Storage Mechanisms**

#### Static

#### Dynamic (charge-based)

#### **Sizing Issues**

Nov-8-10 E4.20 Digital IC Design Topic 8 - 10

#### Making a Dynamic Latch Pseudo-Static

Nov-8-10 E4.20 Digital IC Design Topic 8 - 11 Nov-8-10 E4.20 Digital IC Design Topic 8 - 12

#### **Master-Slave Static Flip-flop**

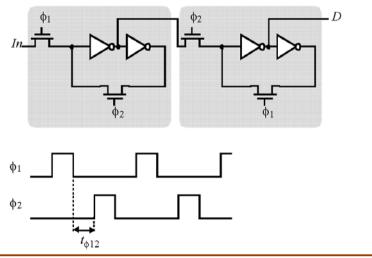

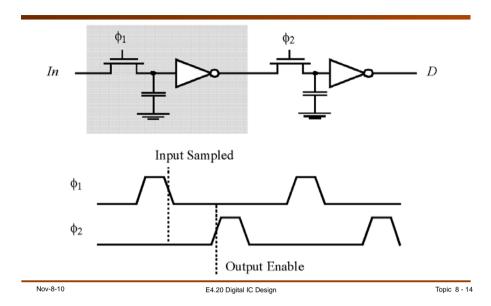

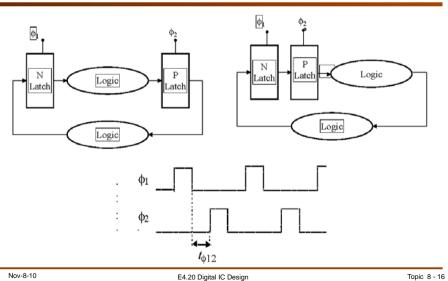

### Use 2-phase non-overlapping clocks

E4.20 Digital IC Design

Nov-8-10

### Two-phase dynamic flip-flop

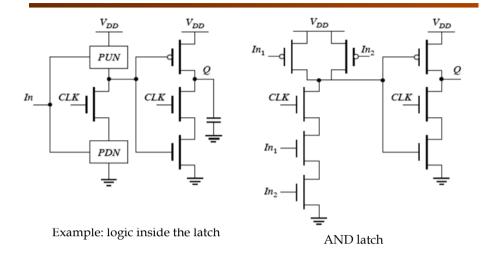

#### Latch + Logic

Nov-8-10 E4.20 Digital IC Design Topic 8 - 15 Nov-8-10 E4.20 Digital IC Design

Topic 8 - 13

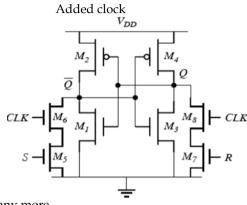

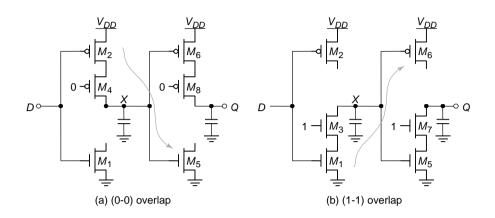

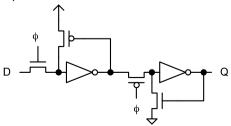

#### Other Latches/Registers: C<sup>2</sup>MOS

# $CLK \rightarrow M_4$ $CLK \rightarrow M_4$ $M_5$ $CLK \rightarrow M_5$ $M_5$ $M_7$ $M_7$

"Keepers" can be added to make circuit pseudo-static

Nov-8-10 E4.20 Digital IC Design Topic 8 - 17

#### **Pipelining**

Reference

| Clock<br>Period | Adder                           | Absolute<br>Value | Logarithm         |

|-----------------|---------------------------------|-------------------|-------------------|

| 1               | $a_1 - b_1$                     |                   |                   |

| 2               | $a_2 + b_2$                     | $ a_1 + b_1 $     |                   |

| 3               | $a_3 + b_3$                     | $ a_2 + b_2 $     | $\log( a_1+b_1 )$ |

| 4               | $a_4 + b_4$                     | $ a_3 + b_3 $     | $\log( a_2+b_2 )$ |

| 5               | a <sub>5</sub> + b <sub>5</sub> | $ a_4 + b_4 $     | $\log( a_3+b_3 )$ |

Pipelined

#### **Insensitive to Clock-Overlap**

Nov-8-10 E4.20 Digital IC Design Topic 8 - 18

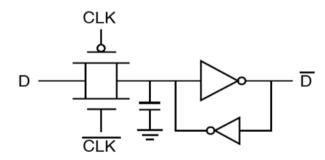

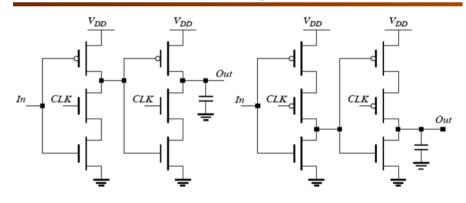

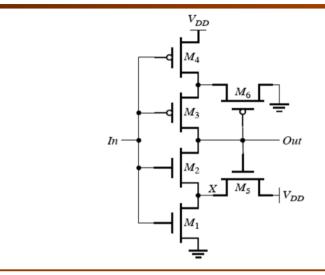

#### **Other Latches/Registers: TSPC**

Positive latch (transparent when CLK= 1)

Negative latch (transparent when CLK= 0)

Nov-8-10 E4.20 Digital IC Design Topic 8 - 19 Nov-8-10 E4.20 Digital IC Design Topic 8 - 20

#### **Including Logic in TSPC**

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 21

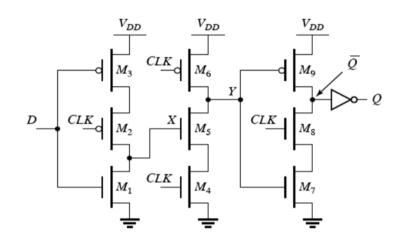

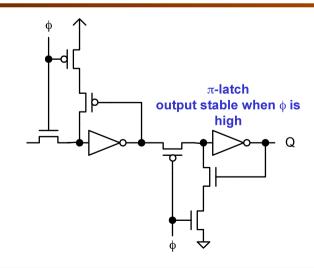

#### $\mu\text{--}\pi$ latches: Poor man's TSPC Latch

What is wrong with this TSPC Latch?

Second attempt:

#### **TSPC** Register

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 22

#### $\mu$ - $\pi$ latches Final solution

Nov-8-10 E4.20 Digital IC Design Topic 8 - 23 Nov-8-10 E4.20 Digital IC Design Topic 8 - 24

## **Pulse-Triggered Latches An Alternative Approach**

#### Ways to design an edge-triggered sequential cell:

Master-Slave Latches

Pulse-Triggered Latch

Nov-8-10 E4.20 Digital IC Design Topic 8 - 25

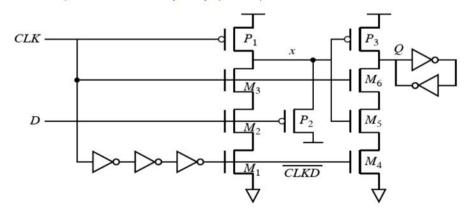

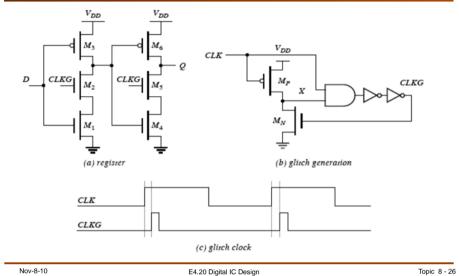

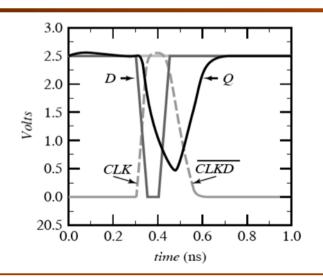

#### **Pulsed Latches**

#### Hybrid Latch - Flip-flop (HLFF), AMD K-6 and K-7:

#### **Pulsed Latches**

2 1.20 Signal to 2001gm

#### **Hybrid Latch-FF Timing**

Nov-8-10 E4.20 Digital IC Design Topic 8 - 27 Nov-8-10 E4.20 Digital IC Design Topic 8 - 28

#### **Latch-Based Pipeline**

# CLK CLK

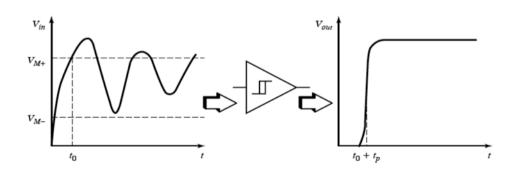

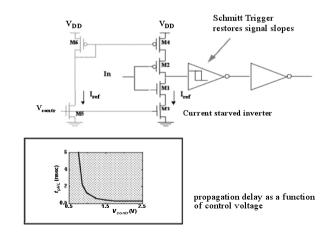

#### **Noise Suppression using Schmitt Trigger**

E4.20 Digital IC Design

Nov-8-10

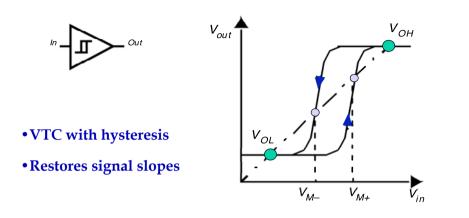

#### Non-Bistable Sequential Circuits— Schmitt Trigger

Nov-8-10 E4.20 Digital IC Design Topic 8 - 30

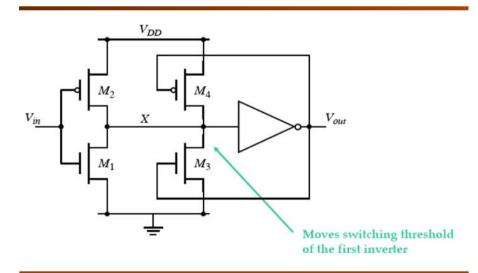

#### **CMOS Schmitt Trigger**

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 31

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 32

Topic 8 - 29

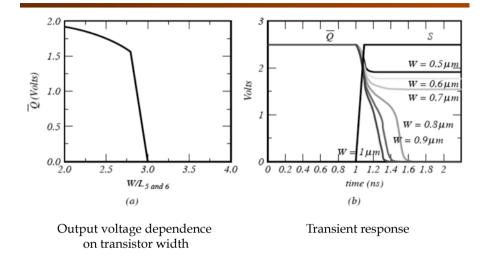

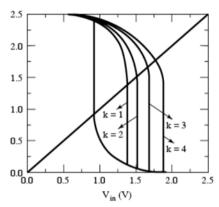

#### **Schmitt Trigger Simulated VTC**

####

The effect of varying the ratio of the PMOS device  $M_4$ . The width is k\*0.5 mm.

Nov-8-10 E4.20 Digital IC Design Topic 8 - 33

#### **Multivibrator Circuits**

**Bistable Multivibrator** flip-flop, Schmitt Trigger

**Monostable Multivibrator** one-shot

**Astable Multivibrator** oscillator

#### **CMOS Schmitt Trigger (2)**

Nov-8-10 E4.20 Digital IC Design Topic 8 - 34

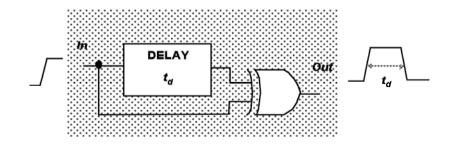

#### **Transition-Triggered Monostable**

Nov-8-10 E4.20 Digital IC Design Topic 8 - 35 Nov-8-10 E4.20 Digital IC Design Topic 8 - 36

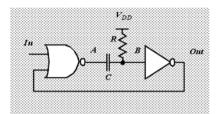

#### **Monostable Trigger (RC-based)**

(a) Trigger circuit.

(b) Waveforms.

Nov-8-10

E4.20 Digital IC Design

Topic 8 - 37

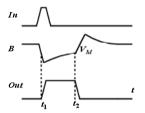

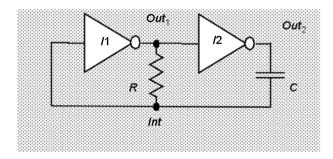

#### **Astable Multivibrators (Oscillators)**

simulated response of 5-stage oscillator

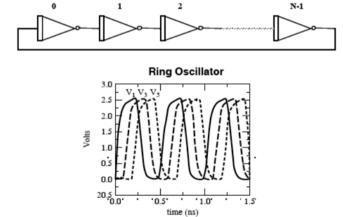

#### **Relaxation Oscillator**

$$T = 2 (log3) RC$$

Nov-8-10 E4.20 Digital IC Design Topic 8 - 38

#### **Voltage Controller Oscillator (VCO)**

Nov-8-10 E4.20 Digital IC Design Topic 8 - 39 Nov-8-10 E4.20 Digital IC Design Topic 8 - 40

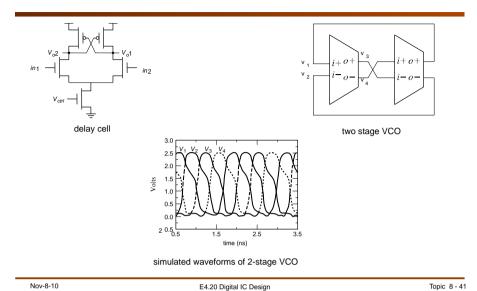

#### **Differential Delay Element and VCO**